#### Imperial College London

Lecture 16 (Supplementary)

spi2dac.v Explained

Peter Cheung

Department of Electrical & Electronic Engineering

Imperial College London

URL: www.ee.imperial.ac.uk/pcheung/teaching/E2\_CAS/ E-mail: p.cheung@imperial.ac.uk

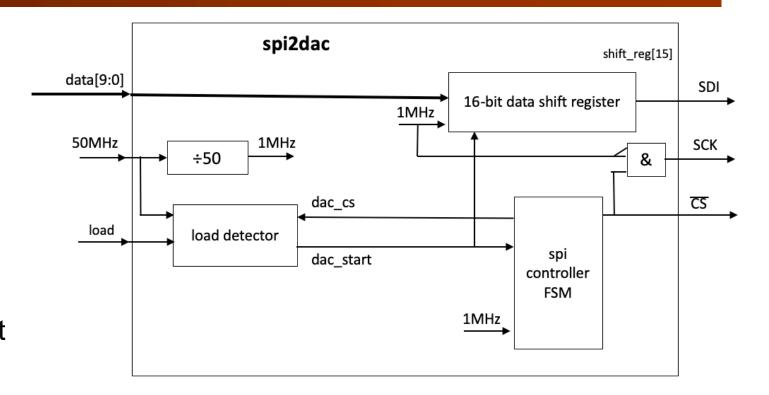

# Spi2dac.v design overview

- The components inside spi2dac are:

- Clock divider

- Load detector to detect load pulse

- 3. FSM to control the spi interface

- 4. Parallel to serial shift register to shift OUT the command and data to the DAC

- Various gates e.g. inverters and AND gates

- Note that the Verilog code is designed to match the block diagram shown here

- It consists of TWO state machines, a counter and a shift register

## The 1MHz clock generator

clk\_1MHz <= ~clk\_1MHz; // toggle the output clock for sd

// ---- end internal 1MHz symmetical clock generator -----

```

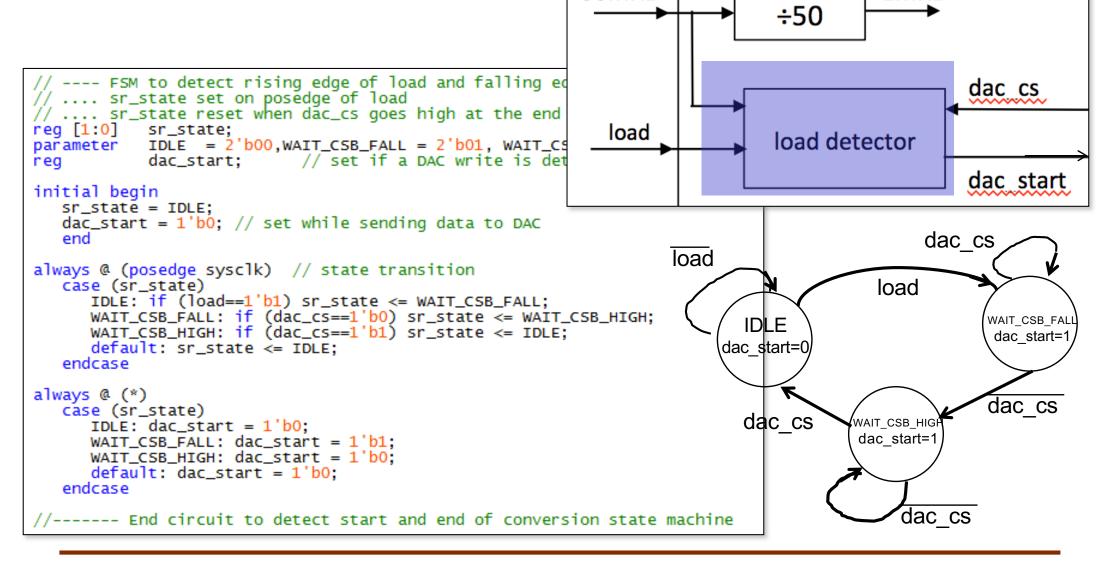

dac cs

load

// --- internal 1MHz symmetical clock generator ---

load detector

clk_1MHz; // 1Mhz clock derived from

req

reg [4:0]

// internal counter

ctr:

dac start

parameter TC = 5'd24; // Terminal count - change

initial begin

clk_1MHz = 0; // don't need to reset - don't care

ctr = 5'b0: // ... Initialise when FPGA is confi

end

always @ (posedge sysclk)

```

50MHz

end else

if (ctr==0) begin ctr <= TC;

ctr <= ctr - 1'b1;

1MHz

÷50

## The load pulse detector

50MHz

1MHz

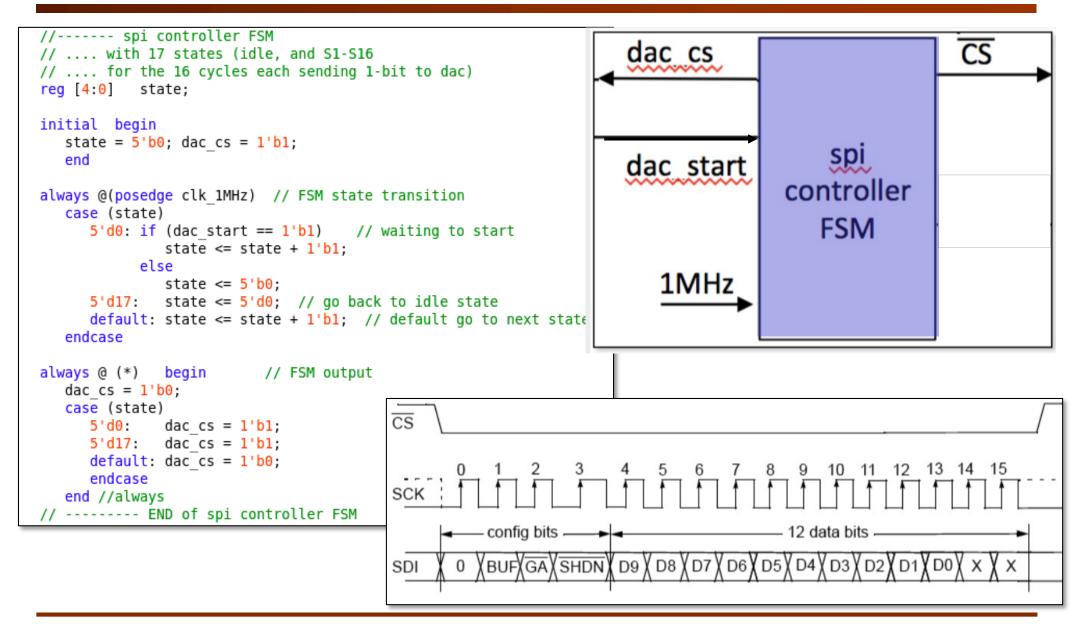

#### The SPI Controller FSM

### The data shift register

```

BUF=1'b1:

// 0:no buffer, 1:vref buffered

parameter

GA N=1'b1:

// 0:gain = 2x, 1:gain = 1x

parameter

// 0:power down, 1:dac active

SHDN_N=1'b1;

parameter

wire [3:0] cmd = \{1'b0,BUF,GA_N,SHDN_N\}; // wire to VDD or GND

// shift register for output data

reg [15:0] shift_reg;

initial begin

shift reg[15]

shift_reg = 16'b0:

data[9:0]

SDI

end

16-bit data shift register

1MHz

always @(posedge clk_1MHz)

if((dac_start==1'b1)&&(dac_cs==1'b1))

SCK

shift_reg <= {cmd,data_in,2'b00};

dac start

else

shift_reg <= {shift_reg[14:0],1'b0};

Assign outputs to drive SPI interface to DAC

assign dac_sck = !clk_1MHz&!dac_cs;

assign dac_sdi = shift_reg[15];

CS

config bits

0 \(\bur\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\bar\)\(\b

SDI

LDAC

```